This repository contains all the information about RISC V CPU Core that is builtin the 5-days Workshop “RISC-V based Microprocessor for You in Thirty Hours"

- Day - 1 : Introduction to RISC-V ISA and GNU compiler toolchain

- Day - 2 : Introduction to ABI and basic verification flow

- Day - 3 : Digital Logic with TL-Verilog and Makerchip

- Day - 4 : Basic RISC-V CPU micro-architecture

- Day - 5 : Complete Pipelined RISC-V CPU micro-architecture/store

- Understanding of RISC V ISA

- RISC V GNU Toolchain

- TL-Verilog

- Designing the Digital Circuits using TL-Verilog

- RISC V RV32I microarchitecture

RISC V ISA RISC V is an open and free Instruction Set Architecture(ISA) which is enabling the modern processor design.RISC V ISA avoids over-architecting for a particular implementation technology and microarchitecture style.RISC V ISA is divided into base integer ISA and optional standard extensions such as Integer Multiplication and Division, Atomic Instructions,Single and Double Precision Floating Points which helps general purpose software development.

RISC V GNU Toolchain

- To compile with RISC-V GCC compiler:

riscv64-unknown-elf-gcc <compiler option -O1 ; Ofast> <ABI specifier -lp64; -lp32; -ilp32> <architecture specifier -RV64 ; RV32> -o <object filename> <C filename>

- To view the disassembly aka assembly code - RISC V :

riscv64-unknown-elf-objdump -d <object filename> | less

In the workshop SPIKE RISC V ISA Simulator is used. More on Spike Simulator Visit https://github.com/riscv/riscv-isa-sim

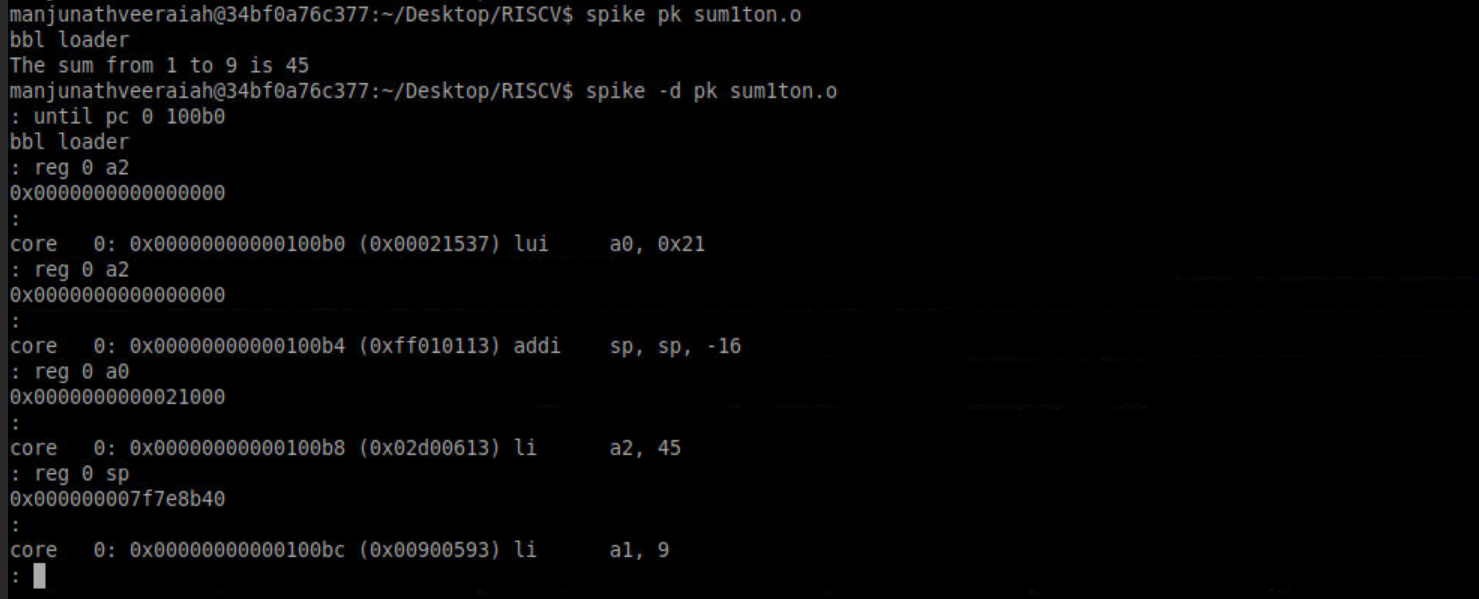

In this picture we can get to know the contents of any register by:

reg 0 "ABI name of register"

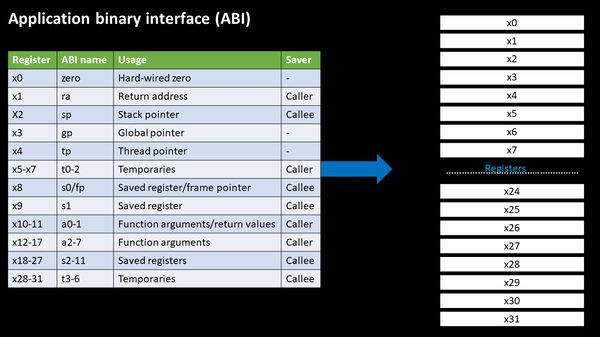

RISC-V architecture has 32 registers. Application programmer, can access each of these 32 registers through its ABI name, for example, you need know the value of stack pointer or move the stack pointer, all you need to do is “addi sp, sp, -16”, where ‘sp’ is the ABI name of stack pointer.

TL-Verilog

Transaction-Level Verilog (TL-Verilog) is an emerging extension to SystemVerilog that supports transaction-level design methodology. In transaction-level design, a transaction is an entity that moves through a microarchitecture.

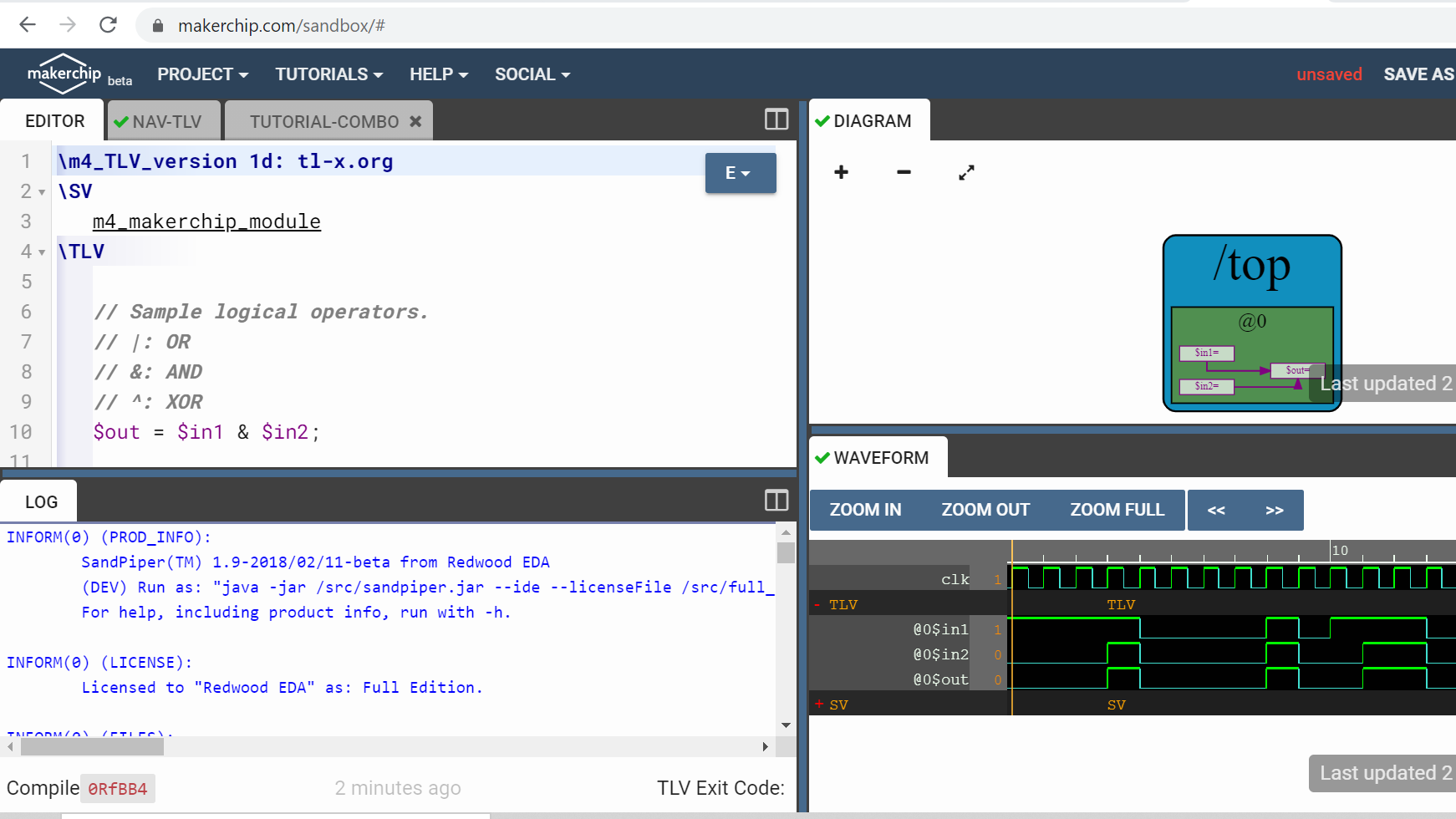

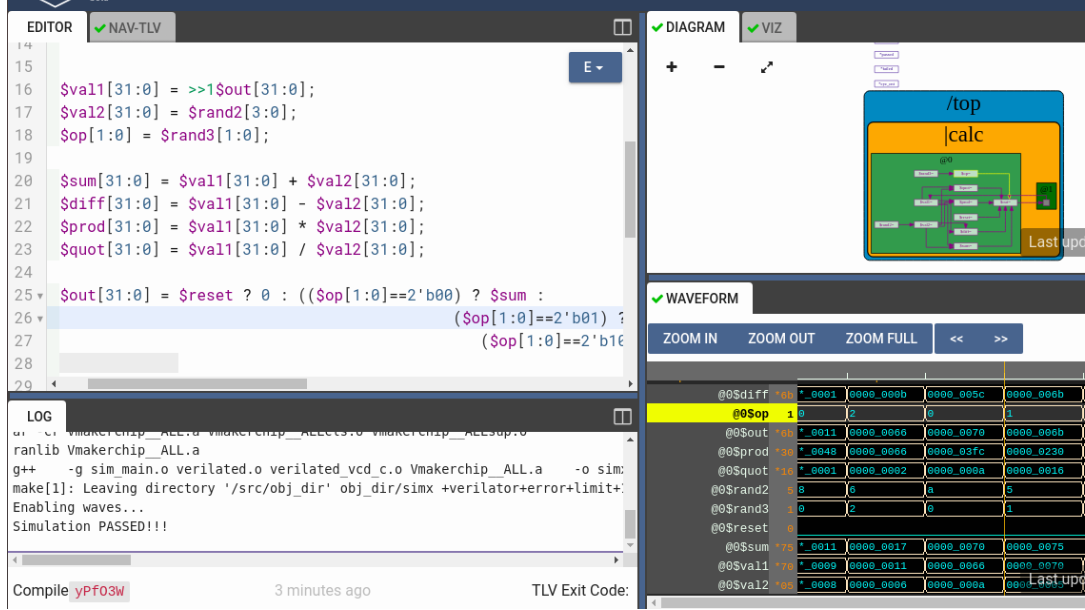

Makerchip IDE

Makerchip is a free online environment for developing high-quality integrated circuits. You can code, compile, simulate, and debug Verilog designs, all from your browser. Your code, block diagrams, and waveforms are tightly integrated.

AND Gate - Makerchip IDE

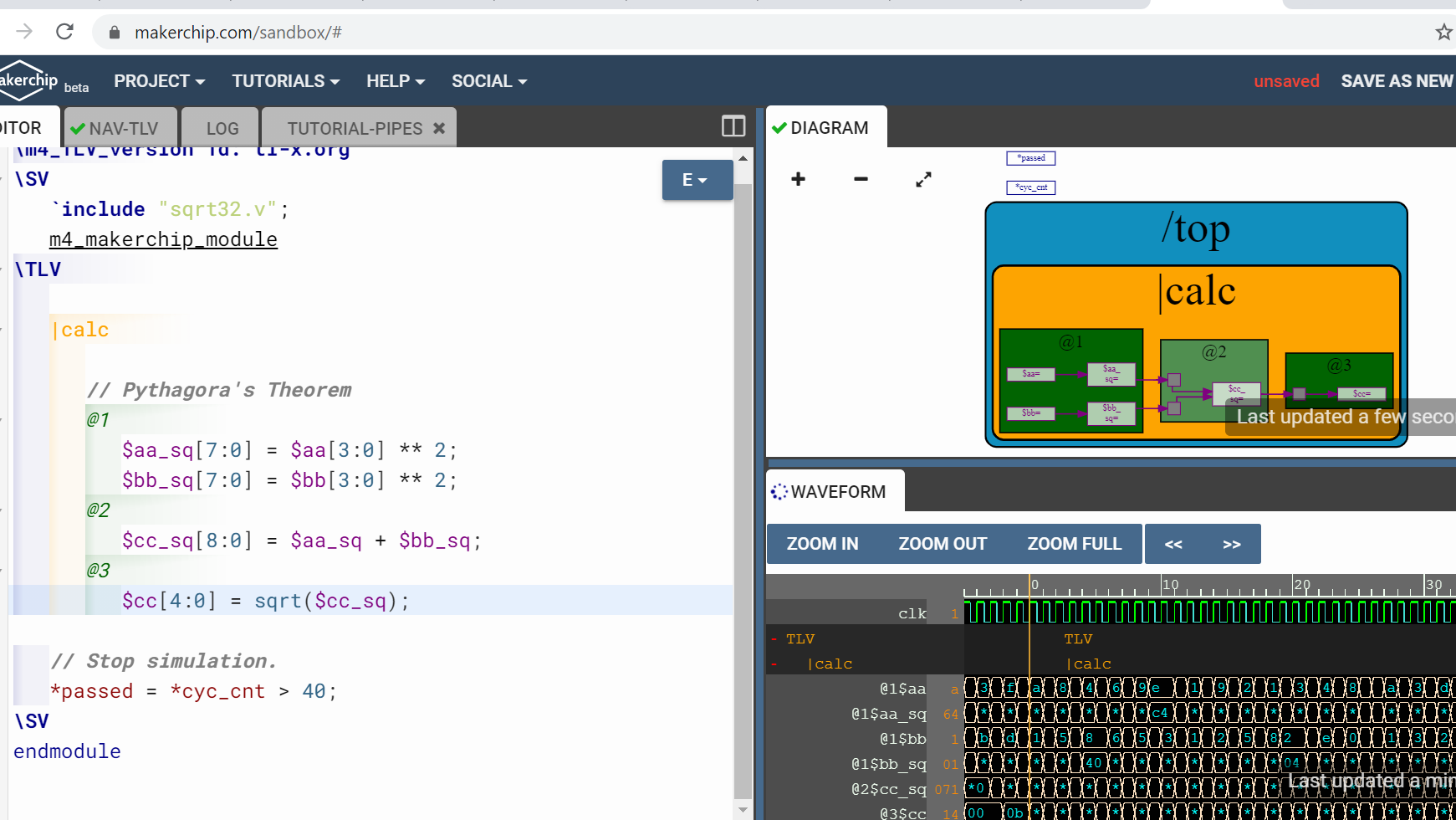

Pipelining in TL-Verilog - Pythagorean Theorem Implementation

- Single Stage pipeline

- 3 - Stage pipeline

Sequential Calculator

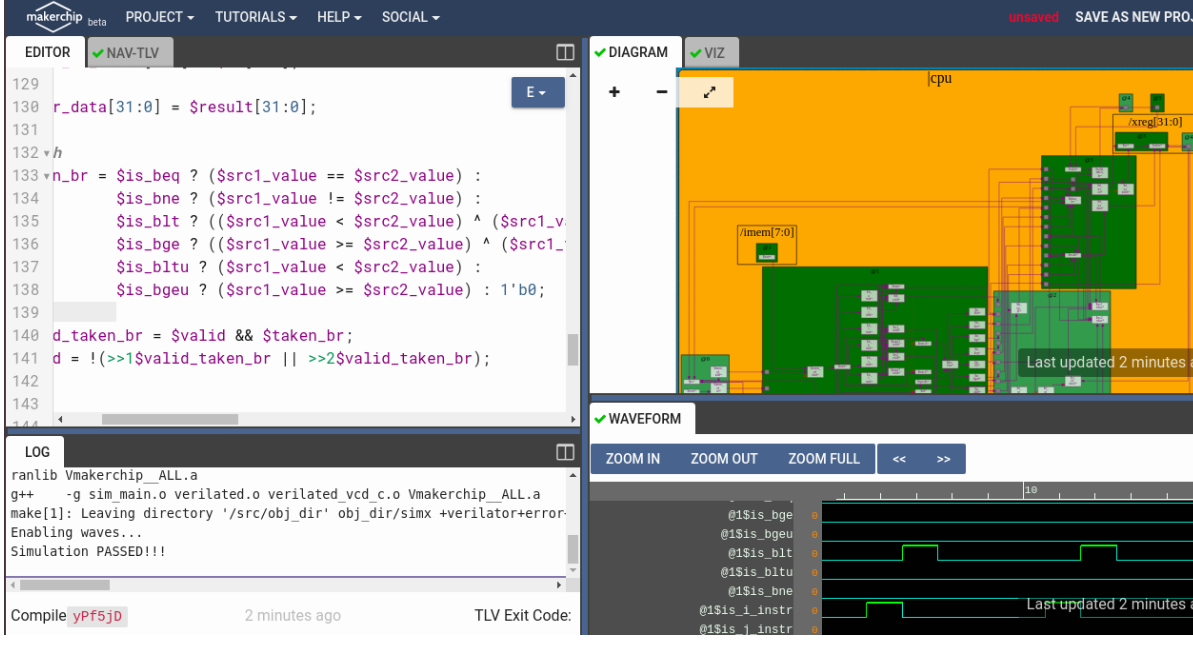

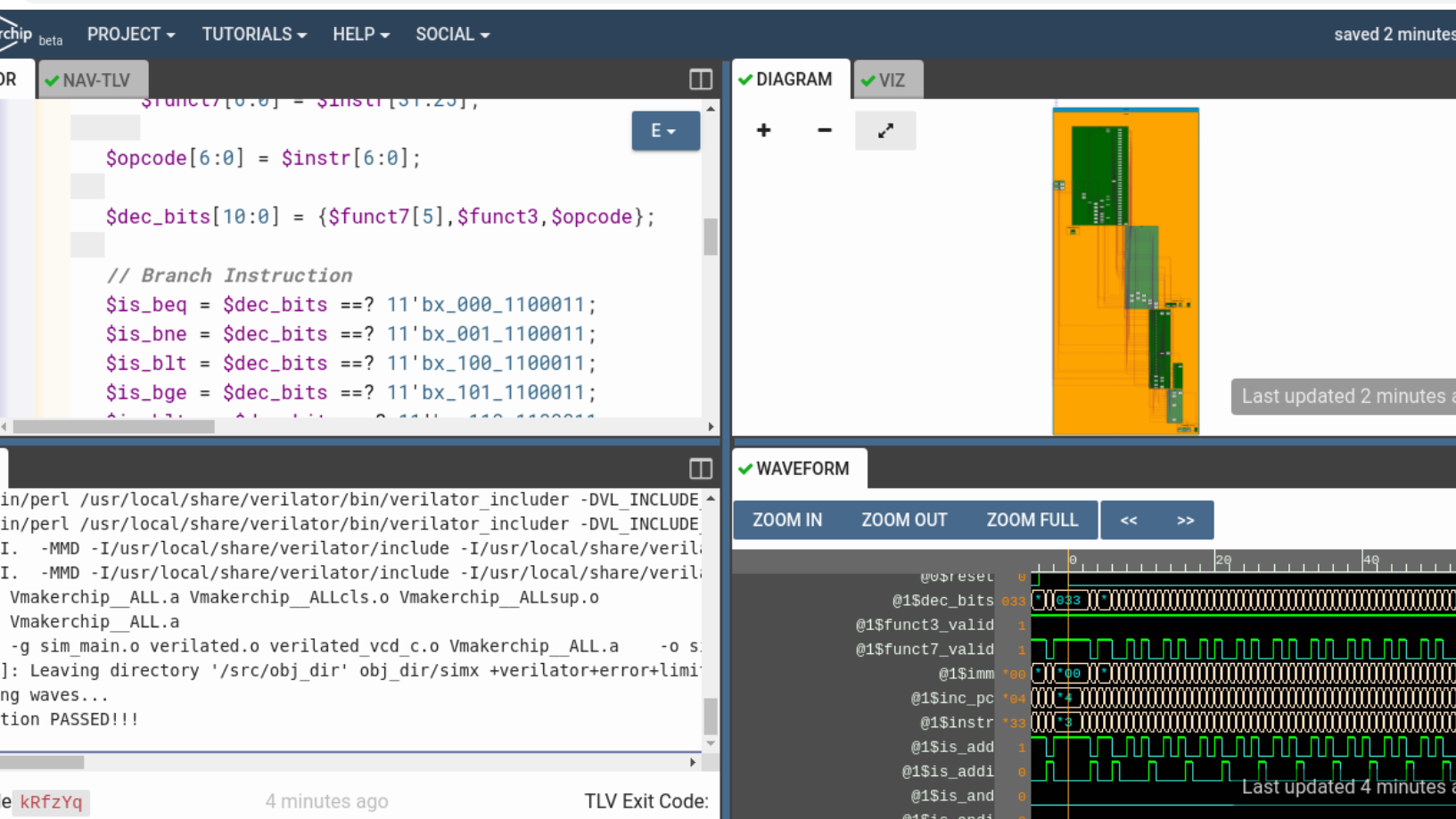

5 stage pipeline processor consists of:

- Instruction Fetch

- Instruction Decode

- Instruction Execute

- Memory Access

- Write Back

- Kunal Ghosh, Co-founder, VSD Corp. Pvt. Ltd.

- Steve Hoover, Founder, Redwood EDA

- Shivam Potdar, GSoC 2020 @fossi-foundation

- Vineet Jain, GSoC 2020 @fossi-foundation