- Jay Patel

- Ben Walker

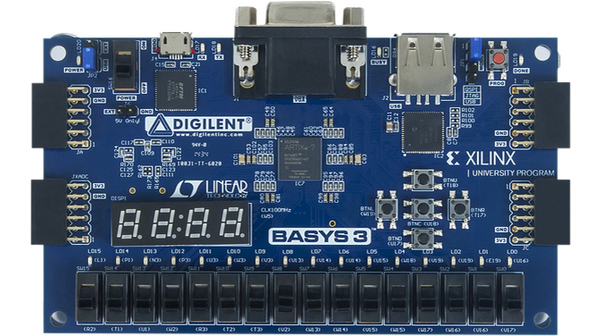

In the project, I and Ben built a digital Clock (24 HR & 12 HR), Quad Seven Segment Display (QSSD) clock, analog clock, jumping and bouncing digital clock. All the clocks except QSSD clock were made to display on a screen through VGA port available on the FPGA board. The QSSD clock was visible on the LEDs present on the FPGA board. The project uses embedded programmed file to manipulate each pixel of the screen. The specification of the screen was 800x600 at 60Hz.

- Xilinx Vivado 2016.2 Webpack Edition

- Font Engine

- FPGA Design and Programming

- Embadded Programming

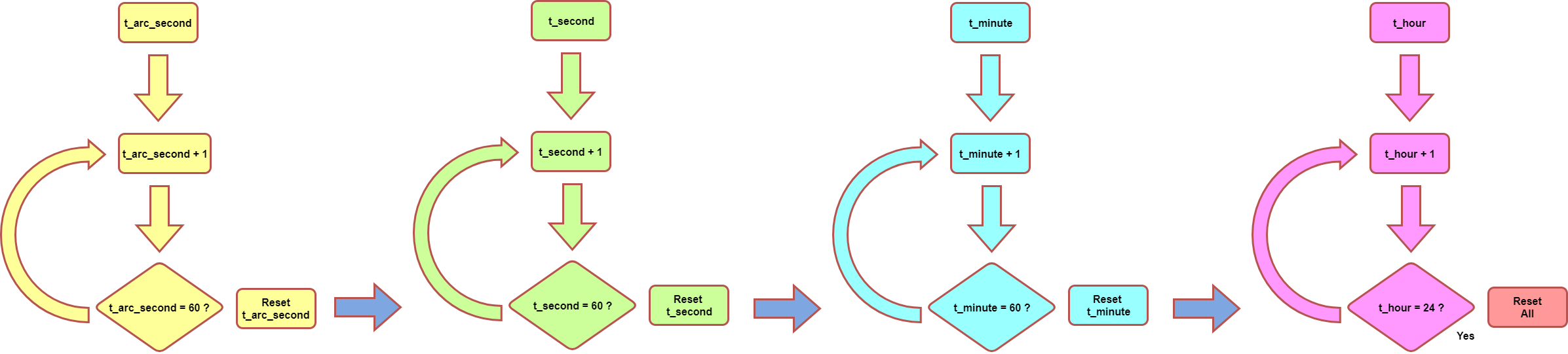

The flowchart of the embedded coding used in .psm file.

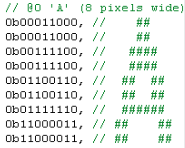

Using font engine, unicode fonts are converted to a binary image similar to ASCII art as shown below.

The screen shots of the outcome of the project.