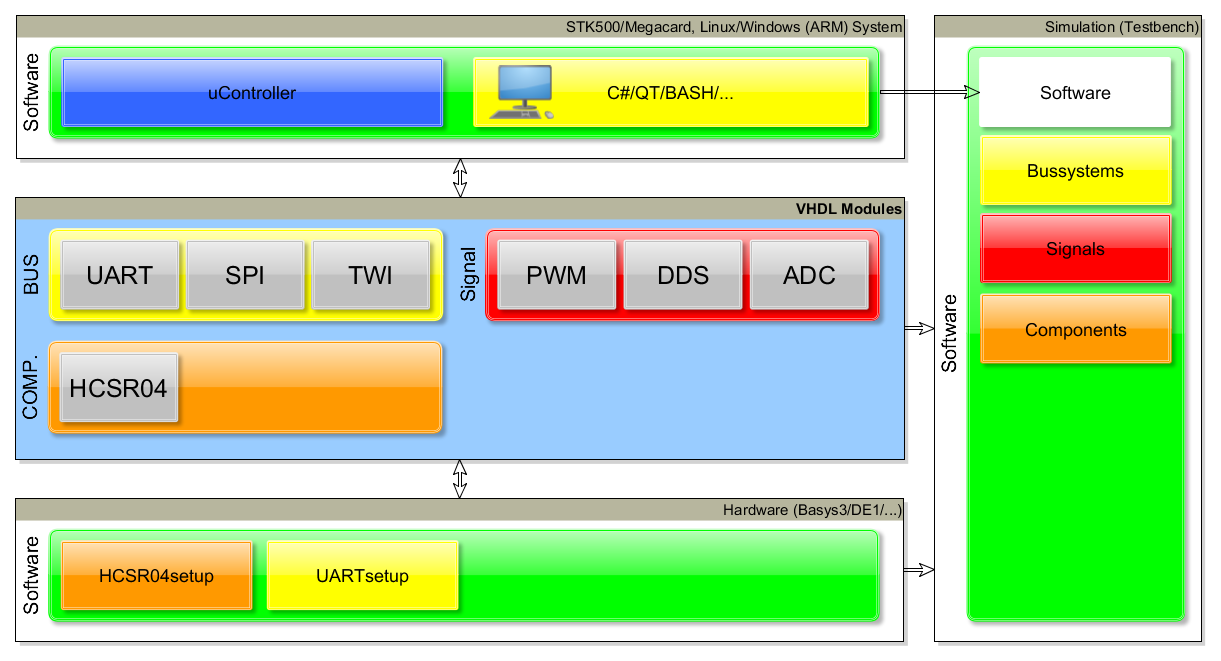

The basys3 repository is a set of VHDL entities and simulations which are used to manage components in the module and other repositories for communication with different microchips and/or semiconductors. It has been written to decrease the amount of commands and/or interrupts @ a microcontroller system. The basys3 repository has got some components which are able to run in standalone mode, no microcontoller will be used or the microcontroller is implemented in the FPGA (VHDL code). There are also some standard logic components like SN74HCTXX or an simple ALU.

- Development Hardware

- Basys3 (Digilent)

- Altera DE1 (Terasic)

- Megacard (HTL-Rankweil)

- Additional Hardware

- Ultrasonic module (HCSR04)

- Development Software

- Atmel Studio (uC C/C++)

- Altera Quartus II (VHDL)

- Xilinx Vivado (VHDL)

Every entity has its own simulation and description (e.g. spi.vhd, spi_tb.vhd and spi.md). Ín the project folder different entities are used for different projects. Additional information can be found in the project.md. We also try to keep our WIKI up-to-date.

- Bus systems

- Components

- Counter

- Divider

- Multiplexer/Demultiplexer

- Signal/Waveforms

- Storage

- Display

In the projects subdirectory there are projects which use some of the above entities. Additional information can be found under the project.md.

This files are valid for all repositories at the SUNriaX Github!

You can find more additional information in the manual repository and/or visit the WIKI for further information (currently under construction).

If there are any further questions feel free to start an issue or contact us, we try to react as quick as possible.

R. GÄCHTER, Rankweil Dec/2017